- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

এপিটাক্সিয়াল স্তর: উন্নত সেমিকন্ডাক্টর ডিভাইসের ভিত্তি

চিত্র 1: ইউনিপোলার ডিভাইসগুলির জন্য ডোপিং ঘনত্ব, স্তরের পুরুত্ব এবং ব্রেকডাউন ভোল্টেজের মধ্যে পারস্পরিক সম্পর্ককে চিত্রিত করে।

SiC এপিটাক্সিয়াল স্তরগুলির প্রস্তুতি প্রাথমিকভাবে বাষ্পীভবন বৃদ্ধি, লিকুইড ফেজ এপিটাক্সি (এলপিই), আণবিক বিম এপিটাক্সি (এমবিই), এবং রাসায়নিক বাষ্প জমা (সিভিডি) এর মতো কৌশলগুলিকে অন্তর্ভুক্ত করে, যেখানে সিভিডি হল কারখানাগুলিতে ব্যাপক উত্পাদনের প্রধান পদ্ধতি।

সারণী 1: প্রধান এপিটাক্সিয়াল স্তর প্রস্তুতির পদ্ধতিগুলির একটি তুলনামূলক ওভারভিউ প্রদান করে।

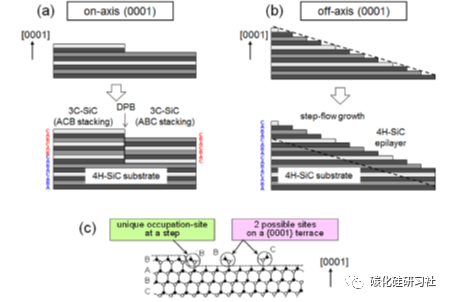

একটি গ্রাউন্ডব্রেকিং পদ্ধতির মধ্যে একটি নির্দিষ্ট কাত কোণে অফ-অক্ষ {0001} সাবস্ট্রেটের বৃদ্ধি জড়িত, যেমন চিত্র 2(b) এ দেখানো হয়েছে। এই পদ্ধতিটি ধাপের আকার হ্রাস করার সময় ধাপের ঘনত্বকে উল্লেখযোগ্যভাবে বৃদ্ধি করে, প্রাথমিকভাবে স্টেপ বাঞ্চিং সাইটগুলিতে নিউক্লিয়েশন সহজতর করে এবং এইভাবে, এপিটাক্সিয়াল স্তরটিকে সাবস্ট্রেটের স্ট্যাকিং সিকোয়েন্সকে নিখুঁতভাবে প্রতিলিপি করার অনুমতি দেয়, পলিটাইপের সহাবস্থানকে দূর করে।

চিত্র 2: 4H-SiC-তে ধাপ-নিয়ন্ত্রিত এপিটাক্সির শারীরিক প্রক্রিয়া প্রদর্শন করে।

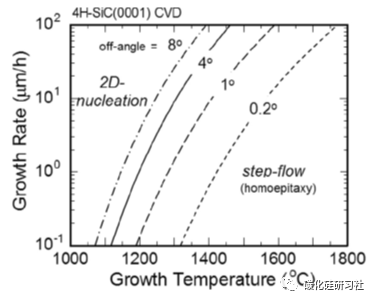

চিত্র 3: 4H-SiC-এর জন্য ধাপ-নিয়ন্ত্রিত এপিটাক্সিতে CVD বৃদ্ধির জন্য জটিল অবস্থা দেখায়।

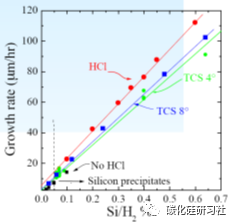

চিত্র 4: 4H-SiC এপিটাক্সির জন্য বিভিন্ন সিলিকন উত্সের অধীনে বৃদ্ধির হার তুলনা করে।

নিম্ন এবং মাঝারি ভোল্টেজ অ্যাপ্লিকেশনের ক্ষেত্রে (যেমন, 1200V ডিভাইস), SiC এপিটাক্সি প্রযুক্তি একটি পরিপক্ক পর্যায়ে পৌঁছেছে, যা বেধ, ডোপিং ঘনত্ব এবং ত্রুটি বিতরণে তুলনামূলকভাবে উচ্চতর অভিন্নতা প্রদান করে, পর্যাপ্তভাবে নিম্ন এবং মাঝারি-ভোল্টেজ SBD-এর প্রয়োজনীয়তা পূরণ করে। , MOS, JBS ডিভাইস এবং অন্যান্য।

যাইহোক, উচ্চ-ভোল্টেজ ডোমেন এখনও উল্লেখযোগ্য চ্যালেঞ্জ উপস্থাপন করে। উদাহরণস্বরূপ, 10000V রেট করা ডিভাইসগুলির জন্য প্রায় 100μm পুরু এপিটাক্সিয়াল স্তরের প্রয়োজন হয়, কিন্তু এই স্তরগুলি তাদের কম-ভোল্টেজ সমকক্ষগুলির তুলনায় যথেষ্ট দরিদ্র পুরুত্ব এবং ডোপিং অভিন্নতা প্রদর্শন করে, সামগ্রিক ডিভাইসের কার্যকারিতার উপর ত্রিভুজাকার ত্রুটিগুলির ক্ষতিকারক প্রভাব উল্লেখ না করে। উচ্চ-ভোল্টেজ অ্যাপ্লিকেশন, যা বাইপোলার ডিভাইসগুলির পক্ষে থাকে, এছাড়াও সংখ্যালঘু ক্যারিয়ারের জীবনকালের উপর কঠোর দাবি রাখে, এই প্যারামিটারটি উন্নত করার জন্য প্রক্রিয়া অপ্টিমাইজেশনের প্রয়োজন হয়।

বর্তমানে, বাজারে 4-ইঞ্চি এবং 6-ইঞ্চি SiC এপিটাক্সিয়াল ওয়েফারের আধিপত্য রয়েছে, বড়-ব্যাসের SiC এপিটাক্সিয়াল ওয়েফারের অনুপাতে ধীরে ধীরে বৃদ্ধি পেয়েছে। SiC এপিটাক্সিয়াল ওয়েফারের আকার মৌলিকভাবে SiC সাবস্ট্রেটের মাত্রা দ্বারা নির্ধারিত হয়। 6-ইঞ্চি SiC সাবস্ট্রেট এখন বাণিজ্যিকভাবে উপলব্ধ, 4-ইঞ্চি থেকে 6-ইঞ্চি SiC এপিটাক্সিতে রূপান্তর ক্রমাগতভাবে চলছে।

যেহেতু SiC সাবস্ট্রেট ফ্যাব্রিকেশন প্রযুক্তির অগ্রগতি এবং উৎপাদন ক্ষমতা প্রসারিত হচ্ছে, SiC সাবস্ট্রেটের খরচ ক্রমান্বয়ে কমছে। প্রদত্ত যে সাবস্ট্রেটগুলি এপিটাক্সিয়াল ওয়েফারের খরচের 50% এরও বেশি জন্য দায়ী, নিম্ন স্তরের দামগুলি SiC এপিটাক্সির জন্য কম খরচের দিকে পরিচালিত করবে বলে আশা করা হচ্ছে, যার ফলে শিল্পের জন্য একটি উজ্জ্বল ভবিষ্যতের প্রতিশ্রুতি রয়েছে।**